PRINSIP KERJA DAN ARSITEKTUR CARA MENEMUKAN KESALAHAN PENGIRIMAN DATA

1. LRC (Logitudional Redundancy Check)

cek redundansi longitudinal (LRC) atau cek redundansi horizontal adalah bentuk

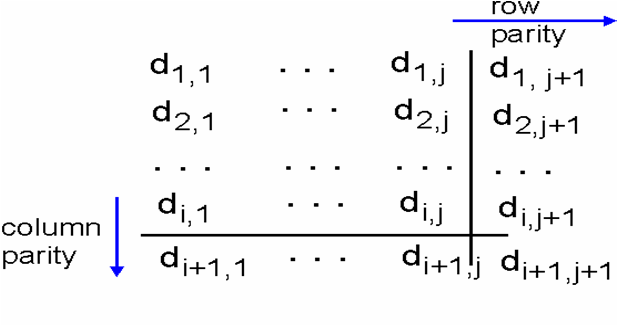

cek redundansi yang diterapkan secara independen untuk masing-masing kelompok paralel bit stream.Teknik Longitudinal Redundancy Check (LRC) ini bisa dikatakan merupakan pengembangan teknik parity check. Pada LRC, data (payload) disusun menjadi sejumlah baris yang ditentukan (blok), kemudian dilakukan perhitungan bit paritas untuk setiap baris dan setiap kolom. Bit paritas baris ditaruh di ujung kanan, sedangkan bit paritas kolom diletakkan dibagian bawah. Sedangkan urutan transmisi dimulai dari kolom paling kiri kearah bawah.

Gambaran LRC dapat dilihat pada gambar dibawah ini:

Untuk

melakukan perhitungan LRC, ditambahkan karakter tambahan (bukan satu bit) di

bagian kiri dan bagian bawah blok :

a.

Block Check Character (BCC) pada tiap blok data. Tiap

bit BCC merupakan pariti dari semua bit dari blok yang mempunyai nomor bit yang

sama. Jadi bit 1 dari BCC merupakan pariti genap dari semua bit 1 karakter yang

ada pada blok tersebut, dan seterusnya

b.

Ditentukan seperti parity, tetapi menghitung secara

longitudinal pada pesan (dan juga secara vertikal)

c.

Kalkulasi berdasarkan pada bit ke-1, ke-2 dst (dari

semua karakter) pada blok menggunakan operator XOR (paritas genap) atau ~XOR

(paritas ganjil) :

·

Bit ke-1 dari BCC ß jumlah 1 pada bit ke-1 dari

karakter

·

Bit ke-2 dari BCC ß jumlah 1 pada bit ke-2 dari

karakter

·

98% laju deteksi error untuk burst errors ( > 10

bit)

·

Mampu mengoreksi error sebuah bit

·

Mampu mengoreksi error sebuah drive yang rusak (dalam

RAID)

·

Perbaikan signifikan dibandingkan parity

checking

Contoh : Akan dilakukan pentransmisian string “DATA” dengan

teknik LRC paritas ganjil. Data tersebut diubah menjadi sebuah blok yang

terbagi menjadi empat baris. Masing-masing karakter direpresentasikan dengan

biner kemudian dihitung paritasnya baik secara longitudinal maupun horizontal.

Ternyata blok yang diterima oleh penerima seperti pada

tabel 1 dibawah ini.

Perhitungan

paritas pada sisi penerima, untuk baris 2 menghasilkan 0 (genap) yang

seharusnya 1 (ganjil) seperti pada baris yang lain. Demikian pula kolom 6

menghasilkan 0 (genap) yang seharusnya 1 (ganjil) seperti pada kolom yang lain.

Jika dua error ini disilangkan maka akan diketahui bahwa error terjadi pada bit

di baris 2 kolom 6.

Koreksi

dilakukan dengan menginversi bit 0 menjadi 1 atau 1 menjadi 0 pada posisi bit

yang baris dan kolomnya dinyatakan error.

Untuk pengecekan error tambahan

byte (atau

kata) ditambahkan ke sebuah blok data untuk mengungkapkan korupsi data. Bit n of this byte indicates whether there was an even or

odd number of "1" bits in bit position n of the bytes in the block. Bit

n byte ini menunjukkan apakah ada jumlah genap atau ganjil dari "1"

bit pada posisi bit n byte di blok tersebut. The

parity byte is computed by XOR ing the data bytes in the block. Paritas

byte dihitung dengan XOR ing

byte data dalam blok. Longitudinal parity allows

single bit errors to be detected. paritas longitudinal

memungkinkan kesalahan-kesalahan bit tunggal untuk dideteksi.

2.

VRC

(Vertical Redundancy Check)

VRC

(Vertical Redundancy Check) Adalah metode

pengecekan eror yang melekat sedikit paritas untuk setiap byte data yang akan

dikirim, yang kemudian di uji untuk menentukan apakah transmisi benar. Metode

ini dianggap agak diandalkan. Jika angka ganjil dari bit yang menyimpang,

periksa tidak akan mendeteksi kesalahan.

Sebuah pengecekan paritas metode sederhana error

kontrol yang digunakan dalam transmisi asinkron dan penyimpanan utama. Lihat

Tabel V-2.VRC memerlukan yang menambahkan sebuah bit paritas pada akhir setiap

karakter atau nilai untuk membuat value.The bit total surat aneh atau bahkan

matematika V, misalnya, dalam ASCII, dikodekan sebagai urutan sedikit 0110101,

yang bahkan jumlah tanda, atau 1 bit. Jika jaringan diatur untuk default

paritas ganjil, bit paritas akan menjadi 1, seperti yang akan membuat byte

delapan-bit dengan, urutan 01.101.011 sehingga menciptakan nilai paritas

ganjil. Atau bit paritas akan menjadi 0 jika jaringan

ditetapkan untuk bahkan paritas, seperti yang akan membuat byte delapan-bit

dengan, urutan 01.101.010 sehingga mempertahankan nilai paritas genap.

Perangkat penerima mengeksekusi proses matematis yang sama untuk memastikan

bahwa nilai bit yang benar total diterima, maka penggunaan istilah redundansi

dan memeriksa. Berbicara dalam hal cara logis di mana manusia menambahkan nomor

fisik diposisikan dalam kolom, kedua perangkat jumlah bit nilai vertikal,

sebagaimana digambarkan dalam tabel berikut, maka penggunaan istilah

vertical.VRC mudah dan murah diterapkan di komputer mempekerjakan transmisi

asynchronous, namun sangat bisa diandalkan, sebagai dua bit errored dalam

karakter menghasilkan suatu kesalahan tidak terdeteksi. Selanjutnya, VRC tidak

memberikan sarana yang melekat pada kesalahan correction.VRC sering dicirikan

sebagai mengirim dan berdoa.

Table 2. Vertical Redundancy Check (VRC).

Bit/Value

|

c o n t r o l

|

1

|

1

|

1

|

0

|

0

|

0

|

1

|

0

|

2

|

1

|

1

|

1

|

0

|

1

|

1

|

0

|

3

|

0

|

1

|

1

|

1

|

0

|

1

|

1

|

4

|

0

|

1

|

1

|

0

|

0

|

1

|

1

|

5

|

0

|

0

|

0

|

1

|

1

|

0

|

0

|

6

|

0

|

0

|

0

|

0

|

0

|

0

|

0

|

7

|

1

|

1

|

1

|

1

|

1

|

1

|

1

|

8 (Parity Ganjil)

|

0

|

0

|

1

|

0

|

0

|

0

|

0

|

3. CRC (Cyclic Redundancy

Check)

CRC (Cyclic Redundancy Check)

adalah algoritma

untuk memastikan integritas data dan mengecek kesalahan pada suatu data yang

akan ditransmisikan atau disimpan.

Data yang hendak

ditransmisikan atau disimpan ke sebuah media penyimpanan rentan sekali

mengalami kesalahan, seperti halnya noise yang terjadi selama proses transmisi

atau memang ada kerusakan perangkat keras. Untuk memastikan integritas data

yang hendak ditransmisikan atau disimpan, CRC dapat digunakan. CRC bekerja

secara sederhana, yakni dengan menggunakan perhitungan matematika terhadap

sebuah bilangan yang disebut sebagai Checksum,

yang dibuat berdasarkan total bit yang hendak ditransmisikan atau yang hendak

disimpan.

Dalam transmisi

jaringan, khususnya dalam jaringan berbasis teknologi Ethernet, checksum akan

dihitung terhadap setiap frame yang hendak ditransmisikan dan ditambahkan ke

dalam frame tersebut sebagai informasi dalam header atau trailer. Penerima

frame tersebut akan menghitung kembali apakah frame yang ia terima benar-benar

tanpa kerusakan, dengan membandingkan nilai frame yang dihitung dengan nilai

frame yang terdapat dalam header frame. Jika dua nilai tersebut berbeda, maka

frame tersebut telah berubah dan harus dikirimkan ulang.

CRC didesain

sedemikian rupa untuk memastikan integritas data terhadap degradasi yang

bersifat acak dikarenakan noise atau sumber lainnya (kerusakan media dan

lain-lain). CRC tidak menjamin integritas data dari ancaman modifikasi terhadap

perlakukan yang mencurigakan oleh para hacker, karena memang para penyerang

dapat menghitung ulang checksum dan mengganti nilai checksum yang lama dengan

yang baru untuk membodohi penerima.

Kode

pendeteksian kesalahan yang paling umum serta paling hebat adalah Cyclic Redundancy Check (CRC) yang

dapat digambarkan sebagai berikut, dengan adanya blok bit k-bit, atau pesan,

transmitter mengirimkan suatu deretan n-bit, disebut sebagai Frame Check

Sequence (FCS), sehingga frame yang dihasilkan, terdiri dari k+n bit, dapat dibagi dengan jelas

oleh beberapa nomor yang sebelumnya sudah ditetapkan. Kemudian receiver membagi

frame yang datang dengan nomor tersebut dan, bila tidak ada sisa, maka

diasumsikan tidak terdapat kesalahan.

Untuk

menjelaskan hal tersebut, kita dapat menggunakan dua cara yaitu:

a.

Modulo 2 Aritmatik

Modulo 2 aritmatik menggunakan penambahan biner tanpa

pembawa, yang hanya merupakan operasi EX-OR saja.

Pengurangan biner tanpa pembawa juga diterjemahkan sebagai operasi EX-OR. Sebagai contoh:

Untuk Gambar Di sini silahakan cari sendiri yach... bukannya aku pelit tapi.. gambarnya aku tdk dapat temukan yang bagus2 mas brow... klik di sini

b.

Polynomials

Cara kedua mengamati proses CRC adalah dengan

menyatakan seluruh nilai sebagai polynomial dalam suatu model variabel X,

dengan koefisien-koefisien

biner. Koefisien berhubungan dengan bit-bit dalam

angka biner. Jadi, untuk M = 110011, kita peroleh M(X) = X5 + X4

+ X + 1, dan untuk P = 11001, kita peroleh p (X) = X4 + X3

+ 1. Operasi aritmetik lagi-lagi berupa

modulo 2. Sekarang, proses CRC digambarkan sebagai:

Untuk Gambar Di sini silahakan

cari sendiri yach... bukannya aku pelit tapi.. gambarnya aku tdk dapat

temukan yang bagus2 mas brow... klik di sini

Error E(X)

hanya akan menjadi tak terdeteksi bila dibagi dengan P(X). Hal ini bisa

ditunjukkan bahwa semua kesalahan berikut ini tidak dibagi dengan pilihan P(X)

yang sesuai dan karenanya mampu dideteksi:

·

Semua bit kesalahan tunggal

·

Semua bit kesalahan ganda, selama P(X) memiliki

sedikitnya tiga 1s

·

Apapun angka kesalahan yang garijil, selama P(X)

memuat faktor (X + 1)

·

Apapun banyaknya kesalahan dimana panjangnya kurang

dari panjang polynomial pembagi; yakni, kurang dari atau setara dengan panjang

FCS.

·

Kesalahan yang besar sekali

Selain itu,

dapat pula ditunjukkan bahwa bila semua pola kesalahan dianggap sama, maka

untuk kesalahan dari panjang r + 1, probabilitas dari kesalahan yang tak

terdeteksi E (X) dibagi

dengan p (X) l adalah 1/2r-1, dan untuk kesalahan yang lebih panjang, probabilitasnya

adalah 1/2r-1, dimana r adalah panjang FCS.

Empat versi

P(X) yang telah digunakan secara luas adalah:

CRC-12

CRC-16

CRC-CCITT

CRC-32

|

= X12 + X11

+ X3 + X2 + X + 1

= X16

+ X15 + X2 + 1

= X16

+ X12 + X5 + 1

= X32

+ X26 + X23 + X22 + X16 + X 12

+ X11+ X10 + X8 + X7 + X5

+ X4

+ X2 + X + 1

|

Sistem CRC-12 dipergunakan untuk transmisi sederatan

sebesar 6-bit karakter dan menbangkitkan 12-bit FCS. Baik CRC-16 maupun CRC-COTT

populer untuk 8-bit karakter, masing-masing di Amerika Serikat dan Eropa, di

mana keduanya sama-sama menghasilkan 16-bit FCS. Nampaknya ini sesuai untuk

sebagian besar aplikasi, meskipun CRC-32 ditentukan sebagai salah satu pilihan

untuk standar transmisi synchronous ujung-ke-ujung.